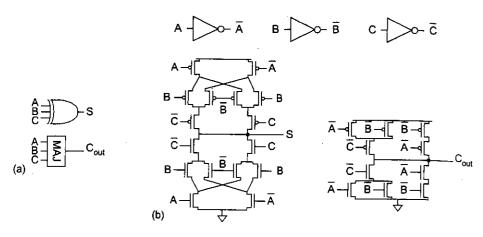

FIG 10.3 Full adder design

Such a design is shown at the gate (a) and transistor (b) levels in Figure 10.4 and uses only 28 transistors. Note that the pMOS network is identical to the nMOS network rather than being the conduction complement. This simplification reduces the number of series transistors and makes the layout more uniform. It is possible because the addition function is *symmetric*, i.e., the function of complemented inputs is the complement of the function.

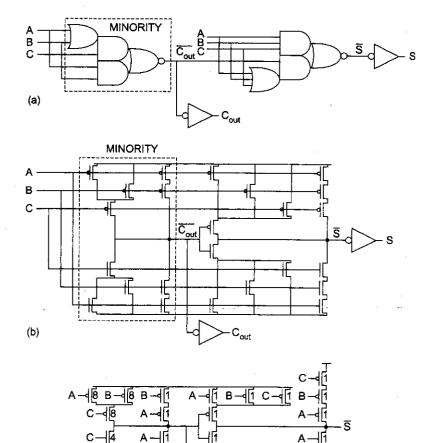

This design has a greater delay to compute S than  $C_{\rm out}$ . In carry-ripple adders (Section 10.2.2.1), the critical path goes from  $C(C_{\rm in})$  to  $C_{\rm out}$  through many full adders, so the extra delay computing S is unimportant. Figure 10.4(c) shows the adder with transistor sizes optimized to favor the critical path using a number of techniques:

- Feed the carry-in signal (C) to the inner inputs so the internal capacitance is already discharged.

- Make all transistors in the sum logic whose gate signals are connected to the carryin and carry logic minimum size (1 unit, e.g.,  $4 \lambda / 2 \lambda$ ). This minimizes the branching effort on the critical path. Keep routing on this signal as short as possible to reduce interconnect capacitance.

- Determine widths of series transistors by logical effort and simulation. Build an asymmetric gate that reduces the logical effort from C to  $\overline{C}_{out}$  at the expense of effort to S.

- Use relatively large transistors on the critical path so that stray wiring capacitance is a small fraction of the overall capacitance.

- Remove the output inverters and alternate positive and negative logic to reduce delay and transistor count to 24 (see Section 10.2.2.1).

FIG 10.4 Full adder for carry-ripple operation

(c)

uses ork or of

tion the

tion

xtra izes

urry-

ıssi-

n

nce

:e

Figure 10.5 shows two layouts of the adder (see also the inside front cover). The choice of the aspect ratio depends on the application. In a standard-cell environment, the layout of Figure 10.5(a) might be appropriate when a single row of nMOS and pMOS transistors is used. The routing for the A, B, and C inputs is shown inside the cell, although it could be placed outside the cell because external routing tracks have to be assigned to these signals anyway. Figure 10.5(b) shows a layout of Figure 10.4(c) that might be appropriate for a datapath. Here, the transistors are rotated and all of the wiring is completed in polysilicon and metal1. This allows metal2 bus lines to pass over the cell horizontally. Moreover, the widths of the transistors can increase without impacting the bit-pitch (height) of the datapath. In this case, the widths are selected to reduce the  $C_{\rm in}$  to  $C_{\rm out}$  delay that is on the critical path of a carry-ripple adder.

В