Download code from drisc.zip

See the results of simulating the following sample code in the simulation output.

LW,1,16 SW,2,20 LI,3,123 LW,4,20 LI,5,-50 LUI,6,16 HALT,,

The file proj.csv contains a test assembly program.

Download project from dsim1.zip

The initial values of memory are read from ram_init.txt.

Reference project report (.qdoc file)

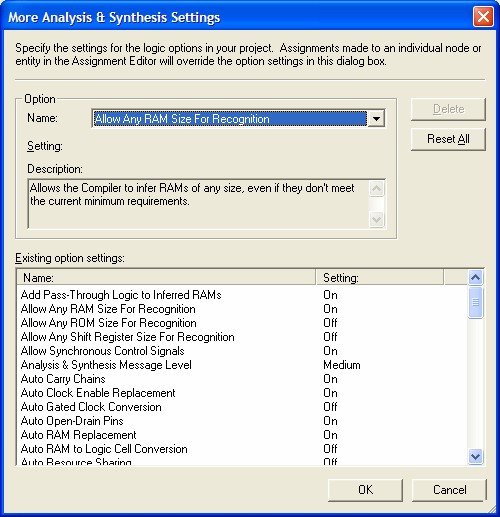

Note: To allow the register file to be implemented in on-chip memory you need to set More Analysis & Sythesis Settings to allow any RAM size for recognition.

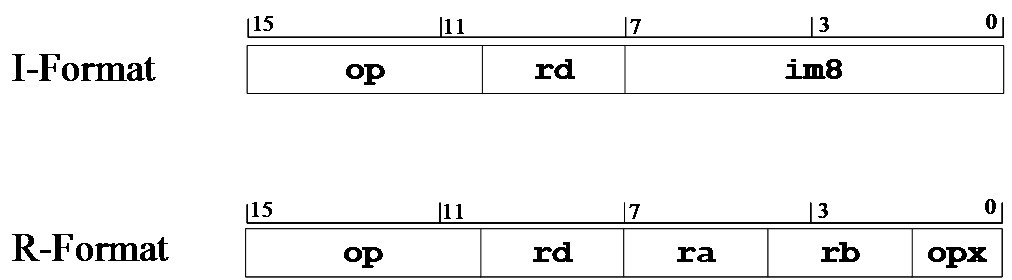

We do not have any R-format instructions yet.

| opcode | name | syntax | action | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | NOP | nop |

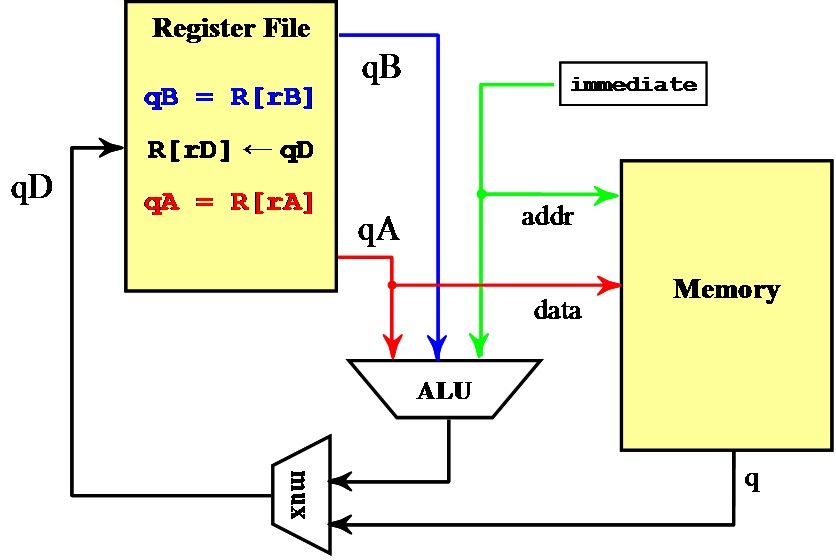

The B register output path is not yet used.

// ALU

wire [15:0] qt = (op_lui? {immed,qa[7:0]}:

(op_li? {se,immed}: 16'h0000));

// writeback register multiplexer

assign qd = (op_lw? q: qt);

Maintained by John Loomis, last updated 1 March 2011